با سلام خدمت دوستان عزیز

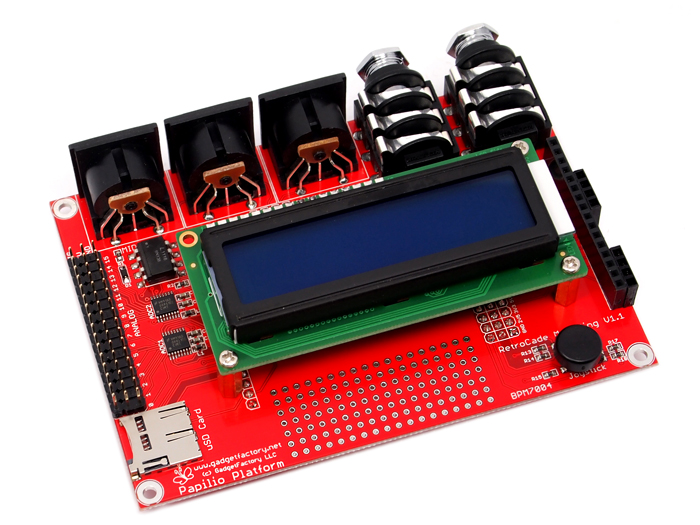

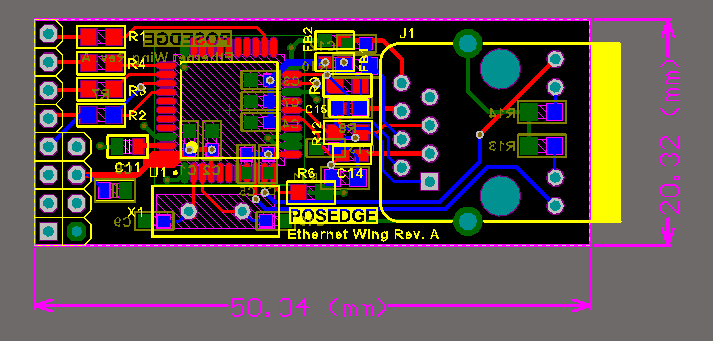

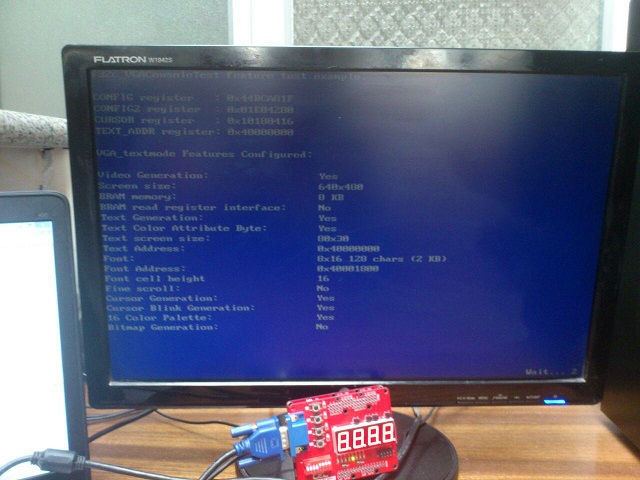

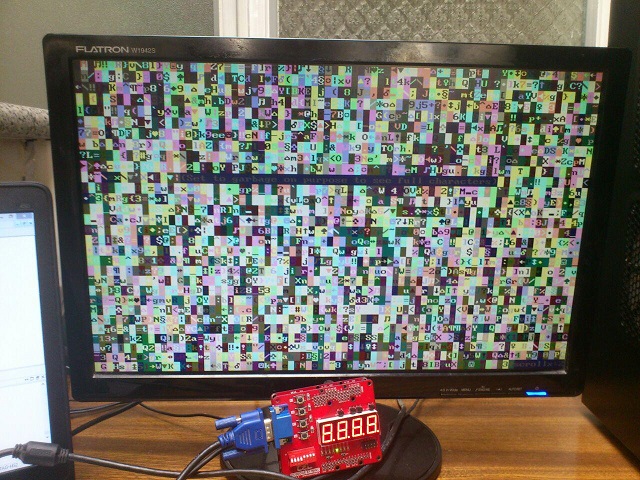

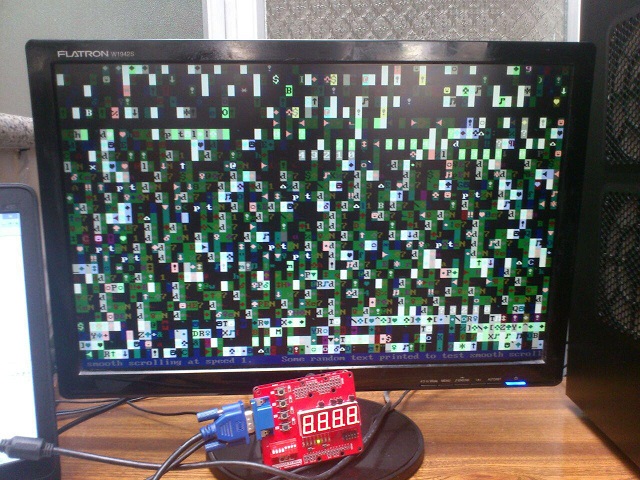

در این پروژه تصویر دوربین OV7670 با استفاده از بال VGA روی مانیتور نمایش داده می شود.

بلوک دیاگرام این پروژه مطابق شکل زیراست.

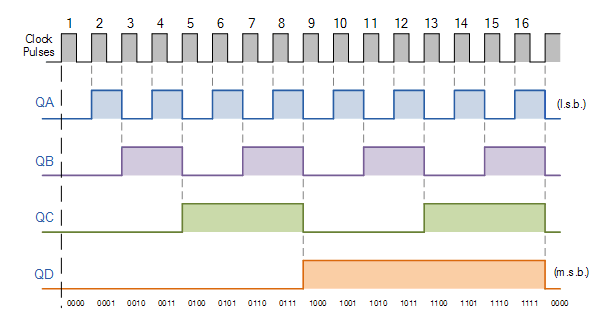

- واحد vga_pll برای تولید کلاک 50MHz و کلاک 25MHz را برعهده دارد. کلاک 25MHz برای واحد VGA و کلاک 50MHz برای سایر واحد ها استفاده میشه. اطلاعات تصویر از سنسور هم با همین کلاک 50MHz دریافت می شود.

- واحد ov7670_controller وظیفه مدیریت پایه های کنترلی سنسور ov7670 را برعهده دارد. همچنین کلاک و ریست این سنسور را تولید می کند و برای تنظیم رجیسترهای سنسور کاربرد دارد.

- واحد ov7670_capture دریافت داده های سنسور را انجام می دهد. داده های سنسور از یک پورت 8 بیتی دریافت می شود ولی اطلاعات یک پیکسل شامل 12 بیت است که این داده ها در طول 2 ارسال از سنسور انجام می شود. این واحد وظیفه دارد در ابتدا اولین پیکسل تصویر را پیدا کرده و بعد از آن با تولید آدرس اطلاعات پیکسل های دریافتی را در یک حافظه رم دو پورت ذخیره می کند.

- واحد Address_Generator وظیفه دارد آدرس مناسب برای خواندن از حافظه رم دو پورت را تولید کند و به واحد RGB ارسال کند.

- واحد RGB در کنار واحد VGA وظیفه تولید سیگنال های تصویر خروجی روی پورت VGA را برعهده دارند.

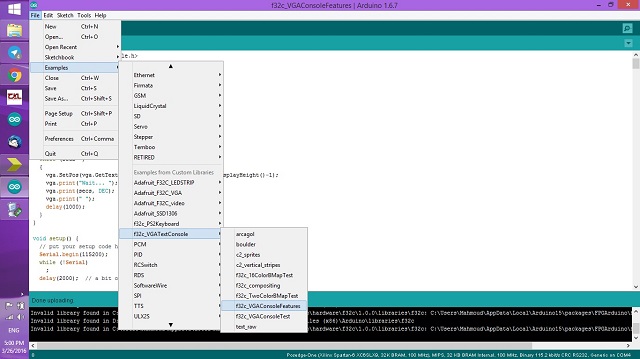

پروژه کامل قابل اجرا روی بورد پازج1 را می تونید از این لینک دانلود کنید.

ویدیو دمو تست سنسور دوربین ov7670 را هم می تونید از این لینک تماشا کنید.

- mahmoud, sigma_mx, M.Sadeghi و 3 فرد دیگر این پست را پسندیده اند

ارسال شده توسط

ارسال شده توسط  ارسال شده توسط

ارسال شده توسط

ارسال شده توسط

ارسال شده توسط