سلام به همه دوستان گل و اساتید گرامی

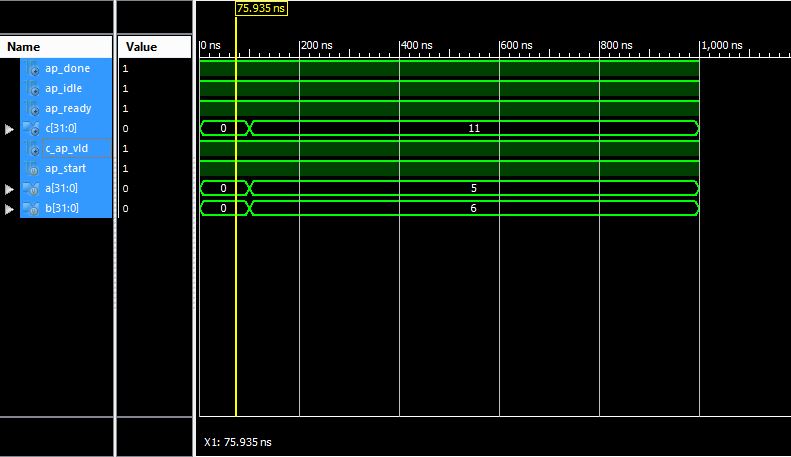

واسه شروع کار تو زمینه HLS یه کد ساده(تابع) به زبان ++C تو محیط vivado hls نوشتم که فقط دوتا عدد رو با همدیگه جمع میکنه .

تابعی که نوشتم اینه :

void su (int a,int b, int *c){

*c = a+b ;

}

و به عنوان testbench هم کد زیرو نوشتم و کامپایل کردم و بدون خطا واسم اجرا شد و نتیجه همون چیزی بود که انتظار داشتم.

#include <stdio.h>

void su (int a,int b,int *c);

int main (){

int m=7;

int n=6;

int result;

su(m,n,&result);

printf("sum of %d and %d is : %d \n",m,n,result);

m=48;

n=56;

su(m,n,&result);

printf("sum of %d and %d is : %d \n",m,n,result);

return 0;

}

بعد از طی کردن این مراحل رفتم سراغ سنتز , سنتز هم انجام شد و کد VHDL واسه من تولید شد.(طبق دونسته های اندک من کدی که تولید میشه خوانایی زیادی نداره که طبیعی هم هست )

حالا تصمیم دارم این کدو توی محیط ISE سنتز کنم یا مثلا به عنوان یه کامپوننت توی یه طراحی استفاده کنم, اما کلی error رنگارنگ syntax داره ![]()

و چون از بعضی از قسمتای کدش سردرنمیارم نمیتونم دستکاریش کنم !

همیشه کدای تولیدی همینجوریه ؟ الان واسه اینکه از این کد استفاده کنم چه کنم !؟

اساتید به دادم برسن ! اولین تجربه من به vivado HLS هستش

اینم از کد تولید شده :

-- ==============================================================

-- RTL generated by Vivado(TM) HLS - High-Level Synthesis from C, C++ and SystemC

-- Version: 2012.2

-- Copyright (C) 2012 Xilinx Inc. All rights reserved.

--

-- ===========================================================

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

library work;

use work.AESL_components.all;

entity su is

port (

a : IN STD_LOGIC_VECTOR (31 downto 0);

b : IN STD_LOGIC_VECTOR (31 downto 0);

c : OUT STD_LOGIC_VECTOR (31 downto 0);

c_ap_vld : OUT STD_LOGIC );

end;

architecture behav of su is

attribute CORE_GENERATION_INFO : STRING;

attribute CORE_GENERATION_INFO of behav : architecture is

"su_inst,su,{component_name=su_inst,HLS_INPUT_TYPE=cxx,HLS_INPUT_FLOAT=0,HLS_INPUT_FIXED=0,HLS_INPUT_PART=xc6slx9tqg144-2,HLS_INPUT_CLOCK=10.000000,HLS_INPUT_ARCH=others,HLS_SYN_CLOCK=2.490000,HLS_SYN_LAT=0,HLS_SYN_TPT=none,HLS_SYN_MEM=0,HLS_SYN_DSP=0,HLS_SYN_FF=0,HLS_SYN_LUT=32}";

constant ap_true : BOOLEAN := true;

constant ap_const_logic_0 : STD_LOGIC := '0';

constant ap_const_logic_1 : STD_LOGIC := '1';

begin

c <= esl_add(b, a);

c_ap_vld <= ap_const_logic_1;

end behav;

پیشاپیش از کمکتون ممنونم ![]()